### Michael Kiperberg

# Preventing Reverse Engineering of Native and Managed Programs

## Michael Kiperberg

## Preventing Reverse Engineering of Native and Managed Programs

Esitetään Jyväskylän yliopiston informaatioteknologian tiedekunnan suostumuksella julkisesti tarkastettavaksi yliopiston Agora-rakennuksen auditoriossa 1 joulukuun 15. päivänä 2015 kello 10.

Academic dissertation to be publicly discussed, by permission of the Faculty of Information Technology of the University of Jyväskylä, in building Agora, auditorium 1, on December 15, 2015 at 10 o'clock.

Preventing Reverse Engineering of Native and Managed Programs

## Michael Kiperberg

Preventing Reverse Engineering of Native and Managed Programs

Editors Timo Männikkö Department of Mathematical Information Technology, University of Jyväskylä Pekka Olsbo, Ville Korkiakangas Publishing Unit, University Library of Jyväskylä

URN:ISBN:978-951-39-6437-5 ISBN 978-951-39-6437-5 (PDF)

ISBN 978-951-39-6436-8 (nid.) ISSN 1456-5390

Copyright © 2015, by University of Jyväskylä

Jyväskylä University Printing House, Jyväskylä 2015

#### **ABSTRACT**

Kiperberg, Michael

Preventing Reverse Engineering of Native and Managed Programs

Jyväskylä: University of Jyväskylä, 2015, 60 p.(+included articles)

(Jyväskylä Studies in Computing

ISSN 1456-5390; 228)

ISBN 978-951-39-6436-8 (nid.)

ISBN 978-951-39-6437-5 (PDF)

Finnish summary

Diss.

One of the important aspects of protecting software from attack, theft of algorithms, or illegal software use is eliminating the possibility of performing reverse engineering. One common method used to deal with these issues is code obfuscation. However, it is proven to be ineffective. Code encryption is a much more effective means of defying reverse engineering, but it requires managing a cryptographic key available to none but the permissible users. The thesis presents a system for managing cryptographic keys in a protected environment and supporting execution of encrypted code. The system has strong security guarantees. In particular, the cryptographic keys are never stored on the target machine, but rather delivered to it from a remote server, upon a successful verification of its authenticity. The keys and the decrypted instructions are protected by a thin hypervisor at all times. The system allows the encryption and execution of both native and Java code.

During native code execution, the decrypted instructions are inaccessible to a potentially malicious code. This is achieved by either preventing execution of any other code or by protecting the memory region containing the decrypted instructions during their execution.

Java programs, unlike native programs, are not executed directly by the processor, but are interpreted (and sometimes compiled) by the Java Virtual Machine (JVM). Therefore, the JVM will require the cryptographic key to decrypt the encrypted portions of Java code, and there is no feasible way of securing the key inside the JVM. The thesis proposes to implement a Java bytecode interpreter inside the secure environment, governed by a thin hypervisor. This interpreter will run in parallel to the standard JVM, both cooperating to execute encrypted Java programs.

Keywords: trusted computing, virtualization, hypervisor, thin hypervisor, Java, remote attestation, interpretation, buffered execution

**Author** Michael Kiperberg

Department of Mathematical Information Technology

University of Jyväskylä

Finland

Supervisors Professor Pekka Neittaanmäki

Department of Mathematical Information Technology

University of Jyväskylä

Finland

Doctor Nezer Zaidenberg

Department of Mathematical Information Technology

University of Jyväskylä

Finland

**Reviewers** Professor Vincenzo Piuri

Department of Computer Science

The University of Milan

Italy

Professor Samuel Itzikowitz

The School of Computer Science

The College of Management

Israel

**Opponent** Doctor Christian Grothoff

Decentralise team

Inria France

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my scientific supervisors, Prof. Pekka Neittaanmäki and Dr. Nezer Zaidenberg, for their guidance, help and moral support throughout the work on this thesis.

I am indebted to the external reviewers of my thesis for their valuable comments and suggestions. I would also like to thank Amit Resh, Asaf Algawi and Roee Leon for co-authoring the joint publications included in this thesis.

I greatly appreciate the support of the COMAS Graduate School, which provided funding for this research. I am also grateful to the Department of Mathematical Information Technology, which financially supported numerous conference trips.

I am thankful to my friends for their moral support and interest in my work. Finally, I wish to thank my parents, Lubov and Yakov, and my brother Arthur, without whom this work would not have been possible, for their love and encouragement.

Jyväskylä November 30, 2015 Michael Kiperberg

### LIST OF FIGURES

| FIGURE 1       | Native code protection system                                | 15 |  |  |  |  |  |

|----------------|--------------------------------------------------------------|----|--|--|--|--|--|

| FIGURE 2       | Java code protection system.                                 | 16 |  |  |  |  |  |

| FIGURE 3       | Relationships between the chapters and the described system  | 18 |  |  |  |  |  |

| FIGURE 4       | Thin hypervisor.                                             | 21 |  |  |  |  |  |

| FIGURE 5       | The attestation protoco.                                     | 27 |  |  |  |  |  |

| FIGURE 6       | The structure of the attestation challenge                   | 28 |  |  |  |  |  |

| FIGURE 7       | Native code protection system                                | 32 |  |  |  |  |  |

| FIGURE 8       | Structure of a Windows PE file.                              | 32 |  |  |  |  |  |

| FIGURE 9       | Example of an encryption process of a single function        | 34 |  |  |  |  |  |

| FIGURE 10      | Example of encrypted function execution                      | 36 |  |  |  |  |  |

| FIGURE 11      | Memory layout during buffered execution                      | 37 |  |  |  |  |  |

| FIGURE 12      | Execution modes                                              | 39 |  |  |  |  |  |

| FIGURE 13      | Relationship between the components of the Java system       | 41 |  |  |  |  |  |

| FIGURE 14      | Structure of Java's class file.                              | 42 |  |  |  |  |  |

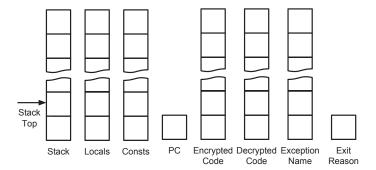

| FIGURE 15      | A simplified control flow during Java's encrypted method ex- |    |  |  |  |  |  |

|                | ecution                                                      | 43 |  |  |  |  |  |

|                |                                                              |    |  |  |  |  |  |

|                |                                                              |    |  |  |  |  |  |

| LIST OF TABLES |                                                              |    |  |  |  |  |  |

|                |                                                              |    |  |  |  |  |  |

| TABLE 1        | Frequencies of uninterpretable instructions                  | 45 |  |  |  |  |  |

|                |                                                              |    |  |  |  |  |  |

#### **CONTENTS**

ABSTRACT

ACKNOWLEDGEMENTS

LIST OF FIGURES AND TABLES

CONTENTS

LIST OF INCLUDED ARTICLES

| 1 | INTRODUCTION        |                                       |    |  |

|---|---------------------|---------------------------------------|----|--|

|   | 1.1                 | Obfuscation                           | 11 |  |

|   |                     | 1.1.1 Instruction Set Architecture    | 12 |  |

|   |                     | 1.1.2 Obfuscation Methods             | 12 |  |

|   |                     | 1.1.3 Breaking Obfuscation            | 12 |  |

|   | 1.2                 | Applicability of Obfuscation          | 13 |  |

|   |                     | 1.2.1 Digital Rights Protection       | 13 |  |

|   |                     | 1.2.2 Military                        | 14 |  |

|   | 1.3                 | Encryption                            | 14 |  |

|   | 1.4                 | Our Method                            | 15 |  |

|   |                     | 1.4.1 Native Code                     | 15 |  |

|   |                     | 1.4.2 Managed Code                    | 16 |  |

|   | 1.5                 | Structure                             | 17 |  |

| 2 | HYI                 | PERVISORS                             | 19 |  |

|   | 2.1                 | Hardware Assisted Virtualization      | 19 |  |

|   | 2.2                 | Thin Hypervisor                       | 20 |  |

|   | 2.3                 | Remote Attestation and Initialization |    |  |

|   | 2.4                 | Thin Hypervisor Protection            | 22 |  |

|   | 2.5                 | Synchronization                       | 24 |  |

| 3 | REM                 | REMOTE ATTESTATION                    |    |  |

|   | 3.1                 | Previous Work                         | 25 |  |

|   | 3.2                 | Our Method                            |    |  |

|   | 3.3                 | Side Effects                          | 28 |  |

| 4 | NA]                 | TIVE CODE EXECUTION                   | 31 |  |

|   | 4.1                 | Encryption Tool                       | 31 |  |

|   | 4.2                 | Encrypted Program Execution           | 33 |  |

|   |                     | 4.2.1 In-place Execution              | 35 |  |

|   |                     | 4.2.2 Buffered Execution              | 36 |  |

|   | 4.3                 | Comparison                            | 38 |  |

| 5 | JAVA CODE EXECUTION |                                       |    |  |

|   | 5.1                 | JVM TI                                | 40 |  |

|   | 5.2                 | System Design                         |    |  |

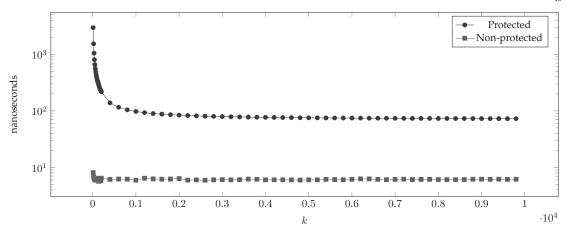

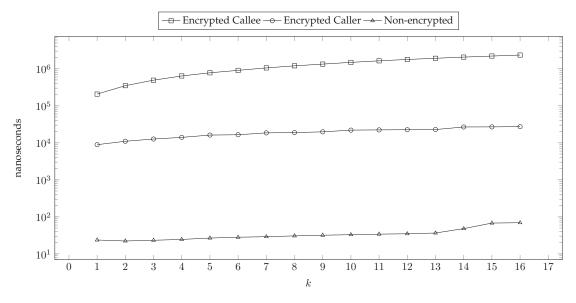

|   | 5.3                 | Measurements                          |    |  |

| 6          | CONCLUSIONS                    |                                                                |                                                    |    |  |  |

|------------|--------------------------------|----------------------------------------------------------------|----------------------------------------------------|----|--|--|

|            | 6.1                            | Contri                                                         | bution                                             | 46 |  |  |

|            | 6.2                            | Limita                                                         | tions and Further Research                         | 47 |  |  |

|            |                                | 6.2.1                                                          | Native Programs                                    | 47 |  |  |

|            |                                | 6.2.2                                                          | Java Programs                                      |    |  |  |

| 7          | SUMMARY OF ORIGINAL ARTICLES 4 |                                                                |                                                    |    |  |  |

|            | 7.1                            | Truste                                                         | d Computing and DRM                                | 48 |  |  |

|            |                                | 7.1.1                                                          | Research Problem                                   | 48 |  |  |

|            |                                | 7.1.2                                                          | Results                                            | 48 |  |  |

|            | 7.2                            | An Eff                                                         | icient VM-based Software Protection                | 49 |  |  |

|            |                                | 7.2.1                                                          | Research Problem                                   | 49 |  |  |

|            |                                | 7.2.2                                                          | Results                                            | 49 |  |  |

|            | 7.3                            | Truly-                                                         | Protect: An Efficient VM-Based Software Protection | 50 |  |  |

|            |                                | 7.3.1                                                          | Research Problem                                   | 50 |  |  |

|            |                                | 7.3.2                                                          | Results                                            | 50 |  |  |

|            | 7.4                            | Efficie                                                        | nt Remote Authentication                           | 50 |  |  |

|            |                                | 7.4.1                                                          | Research Problem                                   | 50 |  |  |

|            |                                | 7.4.2                                                          | Results                                            | 51 |  |  |

|            | 7.5                            | 7.5 Remote Attestation of Software and Execution-Environment i |                                                    |    |  |  |

|            |                                | Mode                                                           | rn Machines                                        | 51 |  |  |

|            |                                | 7.5.1                                                          | Research Problem                                   | 51 |  |  |

|            |                                | 7.5.2                                                          | Results                                            | 52 |  |  |

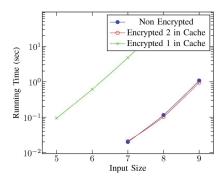

|            | 7.6                            | Systen                                                         | n for Executing Encrypted Java Programs            | 53 |  |  |

|            |                                | 7.6.1                                                          | Research Problem                                   | 53 |  |  |

|            |                                | 7.6.2                                                          | Results                                            | 53 |  |  |

|            | 7.7                            | Systen                                                         | n for Executing Encrypted Native Programs          | 54 |  |  |

|            |                                | 7.7.1                                                          | Research Problem                                   |    |  |  |

|            |                                | 7.7.2                                                          | Results                                            | 54 |  |  |

| YHT        | EEN                            | VETO (                                                         | FINNISH SUMMARY)                                   | 55 |  |  |

| REFERENCES |                                |                                                                |                                                    |    |  |  |

|            |                                |                                                                |                                                    |    |  |  |

INCLUDED ARTICLES

#### LIST OF INCLUDED ARTICLES

- PI Kiperberg, M.; Resh, A.; Zaidenberg, N.J.. Remote Attestation of Software and Execution-Environment in Modern Machines. *The 2nd IEEE International Conference on Cyber Security and Cloud Computing*, 2015.

- PII Zaidenberg, N.J.; Neittaanmäki, P.; Kiperberg, M.; Resh, A.. Trusted Computing and DRM. *Cyber Security: Analytics, Technology and Automation, vol.* 78, pp. 205-212, 2015.

- PIII Kiperberg, M.; Zaidenberg, N.J.. Efficient Remote Authentication. *The Journal of Information Warfare*, vol.12, no.3, 2013.

- PIV Averbuch, A.; Kiperberg, M.; Zaidenberg, N.J.. Truly-Protect: An Efficient VM-Based Software Protection. *Systems Journal*, *IEEE*, vol.7, no.3, pp. 455-466, 2013.

- PV Averbuch, A.; Kiperberg, M.; Zaidenberg, N.J.. An efficient VM-based software protection. *Network and System Security (NSS)*, 2011 5th International Conference, pp. 121-128, 2011.

- PVI Kiperberg, M.; Resh, A.; Algawi, A.; Zaidenberg, N.J.. System for Executing Encrypted Java Programs. *IEEE Transactions on Dependable and Secure Computing*, Submitted.

- PVII Kiperberg, M.; Leon, R.; Resh, A.; Zaidenberg, N.J.. System for Executing Encrypted Native Programs. *IEEE Symposium on Security and Privacy*, Submitted.

The idea of encrypted code execution, which is described in articles [PV] and [PIV], was devised together with Dr. Nezer Zaidenberg. The author designed and implemented the encryption tool and the decryption system, and described their design and performance analysis in articles [PV] and [PIV].

Article [PIII], which was written mainly by the author, discusses the security problems of the system that was presented in articles [PV] and [PIV], and presents possible solutions to those problems. The data presented in the article was collected by the author.

The author devised a hypervisor detection method, which can be embedded into the remote authentication scheme described by Kennell and Jamieson [KJ03]. In addition, the author adapted the remote authentication scheme to multi-core processors. The improvements to the original scheme are described in article [PI], which was written mainly by the author. The co-authors invented and presented the performance counters chaining method.

The author implemented the hypervisor-based decryption system and the encryption tool, as described in article [PVII], which was written mainly by the author. The co-authors implemented the AES decryption scheme and the buffered execution method.

The author devised and designed a system for executing encrypted Java programs. The author implemented the decryption system: both the hypervisor module and the user-mode module. The encryption tool was designed by the author and implemented by the article's co-authors. Article [PVI], which was mainly written by the author, describes the system. The co-authors described the encryption tool.

#### 1 INTRODUCTION

This chapter describes the research area of the thesis, introduces the main concepts, and outlines the structure of the thesis.

One of the important aspects of protecting software from attack, theft of algorithms, or illegal software use is eliminating the possibility of performing reverse engineering. One common method used to deal with these issues is code obfuscation. However, it is proven to be ineffective. Code encryption is a much more effective means of defying reverse engineering, but it requires managing a cryptographic key available to none but the permissible users. The thesis presents a system for managing cryptographic keys in a protected environment and supporting execution of encrypted code. The system has strong security guarantees. In particular, the cryptographic keys are never stored on the target machine, but rather delivered to it from a remote server, upon a successful verification of its authenticity. The keys and the decrypted instructions are protected by a thin hypervisor at all times. The system allows the encryption and execution of both native and Java code.

#### 1.1 Obfuscation

Software obfuscation is a set of techniques used to transform one program into another, such that both have the same semantics but the latter is much harder for a human reader to comprehend. An overview of different obfuscation techniques and other digital rights managements approaches can be found in [PII]. The vendors of obfuscation technologies rarely publish the design of their products, thus preventing their public scrutinization. Nevertheless, some researchers deduce the design of the obfuscating transformation from the resultant program and report their findings in academic press. Usually their reports include not only a detailed description of the transformation but also an outline of the design flaws. Sometimes, the reporters devise an automatic or a semi-automatic tool which is able to reverse the obfuscating transformation.

#### 1.1.1 Instruction Set Architecture

An instruction set architecture (ISA) of a processor is a definition of the capabilities of the processor and the means by which those capabilities can be utilized by a program. In particular, the ISA defines the format and the meaning of each instruction, specifies the arguments of the instruction and the result of its execution.

An ISA can be implemented in hardware, like x86, or in software, like Java bytecode. An execution of a program written for one ISA on a hardware processor of a different ISA is called emulation. Emulation is inherently inferior to direct execution in terms of performance. Nevertheless, it is still widely used in situations where the benefits of emulation (portability, for instance) outweigh its performance penalty. Emulation was extensively studied and two main approaches evolved: interpretation and binary translation. In practice, emulators usually include both an interpreter and a binary translator, and apply each of them where appropriate.

#### 1.1.2 Obfuscation Methods

The most general form of obfuscation, and the one which is generally used in practice, is obfuscation through emulation. The obfuscating transformation translates the original program, in its binary form, to another ISA. The transformation then bundles the transformed code with an emulator of the new ISA. This bundle constitutes the new program, which is then delivered to consumers.

Any ISA allows the performance of operations on immediate values (constants), which are usually supplied as instruction arguments. Obfuscating these values is highly important since they may guide an adversary through the program and lead to its (at least partial) understanding. Many obfuscating transformations translate instructions with immediate values not only by retargeting them at a different ISA, but also by replacing the immediate value with a sequence of instructions whose computation results in this value.

Devising a new ISA for each obfuscating transformation is not practical. Therefore, the obfuscating tools provide only a small set of target ISAs. In addition to the target ISA, the user of such tools can choose a permutation on the instruction encoding, thus making the byte 0x12 mean "addition" according to one permutation, and "multiplication" according to another.

#### 1.1.3 Breaking Obfuscation

Obfuscation based on ISA retargeting is probably the most challenging to break. In fact, even today many malicious programs use this type of obfuscation to prevent their detection by anti-virus and anti-malware software.

Rolles has proposed [Rol09] a method to reconstruct the original program from an obfuscated one. The method has three stages. At the first stage a human adversary studies the obfuscated program, locates the interpreter, and analyzes

it.

The interpreter consists of two main parts: a dispatch loop and instruction handlers. The dispatch loop performs the following three operations until the program terminates: (1) fetch the next instruction, (2) decode it, and (3) dispatch to the correct handler. The instruction handlers modify the internal state of the interpreter according to the required operation. For example, the *add* instruction handler may add the value of one variable to another variable (the variables may represent registers of the emulated ISA). Some optimization may affect this conceptual structure of the interpreter.

At the second stage the human adversary captures the meaning of each instruction handler in a few original ISA instructions. The result of this stage is a dictionary from a previously unknown ISA to the original, known, ISA. This is the last step performed by a human adversary.

The third stage is performed automatically. An automatic tool uses the information gathered by the human adversary to find, in the transformed program, the dispatch loop and the instruction handlers. Then the automatic tool constructs a dictionary from the instruction encodings to the instruction handlers. Together with the dictionary that maps instruction handlers to sequences of original ISA instructions, this information is sufficient to translate the program to the original ISA.

Researchers claim that with additional sophistication of the method described above it is possible to recreate a program whose structure resembles the structure of the original program. We note that human intervention is required only when a new ISA is devised, which requires a human intervention as well, so roughly the same effort is required from the attacking and defending sides.

#### 1.2 Applicability of Obfuscation

Recreation of obfuscated programs requires a modest amount of work. Therefore, obfuscation cannot be used to protect programs of high value, such as military systems (high security value), algo-trading program (high financial value), or even programs of moderately high (financial) value, such as video games.

#### 1.2.1 Digital Rights Protection

Digital content such as games, videos, and the like may be susceptible to unlicensed usage, which has a significant adverse impact on the profitability and commercial viability of such products. Commonly, such commercial digital content may be protected by a licensing verification program; these, however, may be circumvented by reverse engineering the program, which leaves them vulnerable to misuse.

One way of preventing circumvention of the software licensing program, may be using a method of obfuscation. The term obfuscation refers to making

software instructions difficult for humans to understand by deliberately cluttering the code with useless, confusing pieces of additional software syntax or instructions. However, even when changing the software code and making it obfuscated, the content is still readable to the skilled hacker.

Additionally, publishers may protect their digital content product by encryption, using a unique key to convert the software code to an unreadable format, such that only the owner of the unique key may decrypt the software code. Such protection may only be effective when the unique key is kept secured and unreachable to an adversary. Hardware-based methods for keeping the unique key secured are possible [SWP08, Pea02, ELM<sup>+</sup>03], but may have significant deficiencies, mainly due to the investment required in dedicated hardware on the user side — making it costly, and therefore, impractical. Furthermore, such hardware methods have been successfully attacked by hackers [Tar10, Tar12].

Software copy-protection is currently predominantly governed by methodologies based on obfuscation, which are vulnerable to hacking or user malicious activities. There is, therefore, a need for better techniques for protecting sensitive software sections, such as licensing code.

#### 1.2.2 Military

Software produced by military and intelligence organizations may contain sensitive or classified information and algorithms. In this case the potential adversary is well equipped, and is not limited by time or other resources, since it is supported by the government of a hostile state.

Our experience suggests that, generally, the only effective countermeasure is the physical isolation of the software and its environment from a potential adversary. In case of exposure, the software and its environment are physically destroyed, either remotely or by the operator of this software. There are two main disadvantages to this approach. The first is the danger of unintentional activation of the destruction mechanism. The second is the failure to destroy the software when an exposure is detected, either due to the inability of the human operator to trigger the destruction sequence, or failure of the (possibly damaged) destruction mechanism itself. Therefore, a better solution is required — a solution which can guarantee the secrecy of the software information by design, and which does not require any special or dangerous actions.

#### 1.3 Encryption

Traditionally, when a sensitive information has to be placed in a potentially hostile environment, it is first encrypted with a key, which is kept in a trusted environment at all times. Inspection and manipulation of the information requires the key. Previously, researchers suggested [Bes80] a processor architecture that includes a cryptographic module, which can be used to decrypt the instructions as

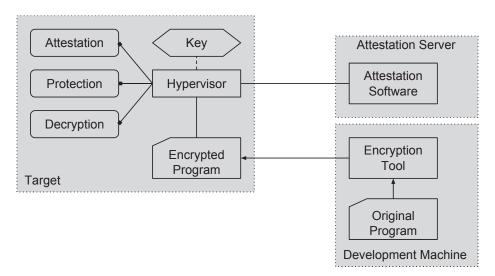

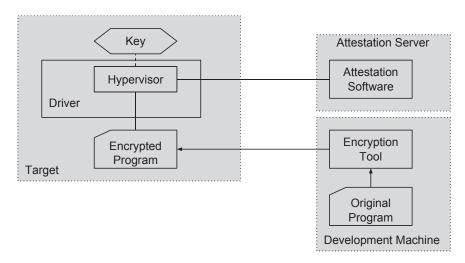

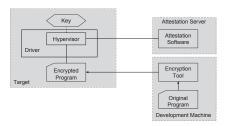

FIGURE 1 Native code protection system. The original program is encrypted before its distribution. The encryption key is stored in the attestation server, which delivers it to the hypervisor in the target machine upon successful attestation. The hypervisor is responsible for decrypting the protected code and protecting itself, the decryption key and the decrypted code from an adversary.

the first step in their execution process. The cryptographic keys are embedded in the processor during the manufacturing process and are known only to the manufacturer. This suggestion is partially realized in modern processors. For example, Intel announced a new extension to their x86 processors, the software guard extension (SGX), which adds cryptographic modules and embeds cryptographic keys that protect a region of memory inside a program from unauthorized access. The protected regions of memory are stored in encrypted form. This extension, by its design, is primarily targeted at data protection rather than code protection, although it is probably possible to use this technology for code protection as well. Unfortunately, SGX is currently unavailable to computer manufacturers and its future availability on the widespread processor families is uncertain.

#### 1.4 Our Method

#### 1.4.1 Native Code

This work provides a detailed description of a native code protection method which is based on encryption and can be implemented on commonplace processors. Our method consists of several components, that together provide protection for both the decryption key and the encrypted program. Figure 1 outlines the relationships between the different components of the system. Conceptu-

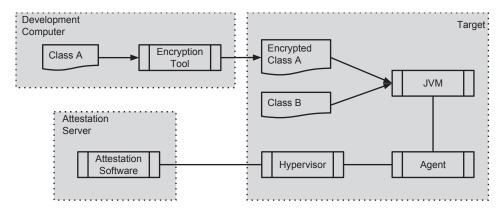

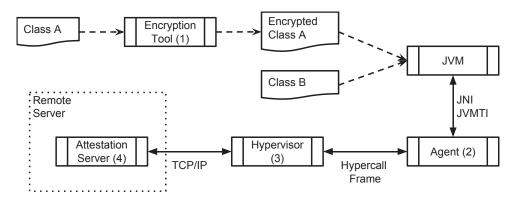

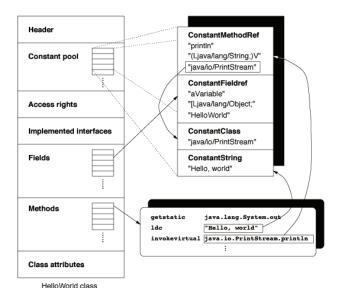

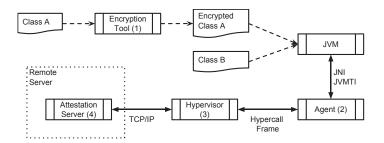

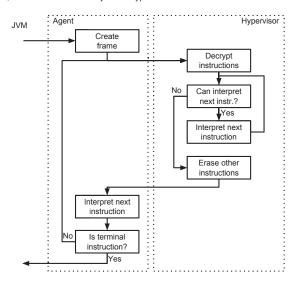

FIGURE 2 Java code protection system. The encryption tool transforms regular Java classes into encrypted ones. Regular and encrypted Java classes are then loaded by the JVM. The JVM loads a JVM TI agent through the JVM TI interface. The agent links the hypervisor to the JVM and assists in the interpretation process. The agent communicates with the JVM through JVM TI and JNI. The communication between the agent and the hypervisor is based on hypercalls and execution frames. The hypervisor receives the decryption key from a remote server, which attests the validity of the hypervisor and the hardware on which it executes.

ally, the components are deployed on three computers. The program is originally compiled on the development machine and encrypted using the encryption tool. Then the program is distributed to consumers, where it gets installed on the target computer. The decryption key is stored in the attestation server, which delivers it to the target computer upon its successful authentication. This scheme was originally described in [PV, PIV].

In addition to the encrypted program, the installation package installs a hypervisor, which has three aspects: attestation, protection, and decryption. The attestation aspect refers to the hypervisor's ability to participate in the remote attestation protocol. The purpose of this protocol is to verify the authenticity of the target hardware and software, and deliver the cryptographic keys from the attestation server to the target computer. The protection and decryption aspects refer to the hypervisor's ability to decrypt programs and execute them while guaranteeing the secrecy of the decrypted instructions and the cryptographic key. The next chapters describe the design and implementation details of the three aspects.

#### 1.4.2 Managed Code

In recent years, programs that are targeted at managed execution environments have become widespread [DKGC07]. Unlike regular (native) programs, managed programs cannot be executed directly by the CPU and, therefore, require a special (native) program to interpret the managed program. Managed execution environments are superior to native environments in memory management, debug-

ging and profiling support. For these reasons, managed execution environments have become popular among developers of desktop and mobile applications.

While it is possible to guarantee that a sequence of native instructions cannot be intercepted (read or modified) during its execution by a CPU, such a guarantee cannot be made for a managed execution environment, since an unexpected behavior can be introduced into the software that implements the managed execution environment. This work describes a technique for executing safely encrypted managed programs on the available managed execution environments.

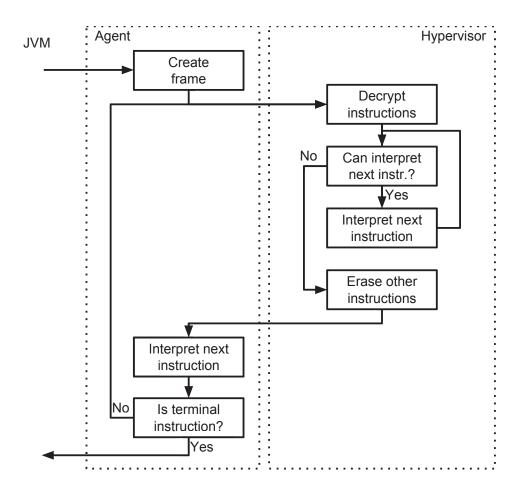

Executing an encrypted managed program is more challenging and this results in a more complex system design, which is captured by Figure 2. Similarly to the design of the native system, this design consists of three conceptual computers: an encryption tool, a hypervisor, and an attestation software. The hypervisor still has the three aspects described above. This system extends the native system by introducing two new components: the JVM, which is the standard execution environment for Java programs, and Agent, which is a JVM TI agent capable of inspecting and modifying the internal state of the program and the JVM.

In order to support near-optimal performance of executing the unencrypted parts of a Java program, the proposed system executes them on a regular JVM. The JVM TI agent intercepts attempts to execute encrypted code and transfers control to the hypervisor. The hypervisor decrypts and executes the code until it reaches an instruction, whose execution requires cooperation with the JVM. At this point, the hypervisor returns control to the JVM TI agent and passes it the decrypted instruction. The JVM TI agent executes the instruction and transfers control back to the hypervisor. In contrast to the native code execution, this design leaks some secret information. This work provides estimates on the amount of leaked information and discusses techniques that can reduce this amount.

#### 1.5 Structure

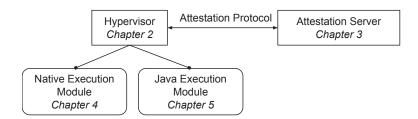

The structure of the thesis is as follows: the next chapter overviews virtualization in general and its applicability to program protection. Chapter 3 presents a remote authentication method capable of authenticating software and hardware of modern machines. Chapters 4 and 5 describe virtualization-based methods for native and Java programs' protection. An overview of the articles included in the thesis is provided in chapter 7. Finally, chapter 6 summarizes the contribution and limitations of the thesis and outlines the directions of further research. Figure 3 depicts the relationships between the chapters and the describe system.

FIGURE 3 Relationships between the chapters and the described system. The attestation server authenticates the hypervisor which embeds either the native execution module or the Java execution module.

#### 2 HYPERVISORS

A hypervisor, also referred to as a Virtual Machine Monitor (VMM), is software, which may be hardware assisted, that manages multiple virtual machines on a single system [PG74]. The hypervisor virtualizes the hardware environment in a way that allows several virtual machines, running under its supervision, to operate in parallel over the same physical hardware platform, without obstructing or impeding each other. Each virtual machine has the illusion that it is running, unaccompanied, on the entire hardware platform. The hypervisor is referred to as the *host*, while the virtual machines are referred to as *guests*.

#### 2.1 Hardware Assisted Virtualization

Hypervisors have been in use as early as the 1960s on IBM mainframe computers [Cre81]. After 2005, Intel and AMD introduced hardware support for virtualization (Intel VT-X [Int07], AMD AMD-V [AMD10]), which allowed the implementing of hypervisors in the ubiquitous PC platforms. There are slight differences between Intel's and AMD's implementation of the x86 virtualization extension. In this work we will discuss only Intel's implementation and mention the differences where they are important for the discussion.

In order to support multiple OS guests, a hypervisor must unobtrusively intercept OS access to hardware resources so it can attend to them itself. The hypervisor can then manage hardware allocations that maintain proper separation between the guests. The guest OS is unaware of the hypervisor's intervention, as it experiences a normal hardware access cycle. The only distinction being the elapsed time, since the hypervisor mediation has a time-toll. This property led to a debate regarding the detectability of a hypervisor [BYDD+10, RT07, RT08, Fer07].

A virtual machine control structure (VMCS) is defined for each virtual environment managed by a virtual machine monitor (VMM). This structure defines the values of privileged registers, the location of the interrupt descriptors table,

and additional values that constitute the internal state of the virtual environment. In addition, this structure defines the events that the VMM is configured to intercept, and the address of the function that should handle the interception. The act of control transfer from the virtual environment to a predefined function is called vm-exit and the act of control transfer from the function back to the virtual environment is called vm-entry. Upon vm-exit the function can determine the reason of the vm-exit by examining the fields of the VMCS and altering them, thus altering the state of the virtual environment as it wishes. Finally, the VMCS can define a mapping between the physical memory as it is perceived by the virtual environment and the actual physical memory. As a consequence, the VMM can prevent access to some physical pages by the virtual environment. Moreover, the virtual environment will be unaware of this situation.

Interception of some events cannot be disabled, while interception of others cannot be enabled. For example, execution of the CPUID instruction always causes a vm-exit, while execution of the SYSCALL instruction never causes a vm-exit. Processors manufactured by AMD allow for disabling of interception for all events.

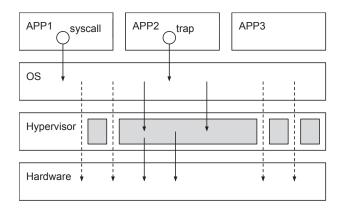

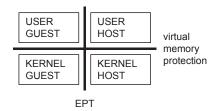

### 2.2 Thin Hypervisor

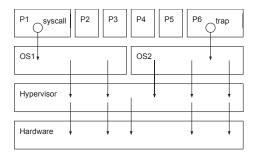

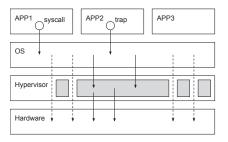

We propose to use a hypervisor for securing a single guest. Rather than wholly virtualizing the hardware platform, a special breed of hypervisor, called a *thin hypervisor*, is used [SET<sup>+</sup>09, CSK10]. A thin hypervisor is configured to intercept only a small portion of events. All other events are processed without interception, directly, by the OS. A thin hypervisor only intercepts the set of events that allows it to protect an internal secret (such as a cryptographic key) and protect itself from subversion. Figure 4 depicts a thin hypervisor supporting a single guest. Since a thin hypervisor does not control most of the OS interaction with the hardware, multiple OS are not supported. On the other hand, system performance is kept at an optimum.

A thin hypervisor facilitates a secure environment by: (a) setting aside portions of memory that cannot be accessed by the guest, (b) storing the cryptographic key in privileged registers, and (c) intercepting privileged instructions that may compromise its protected memory or the cryptographic key.

Once this environment is correctly configured, a thin hypervisor can be utilized to carry out specific operations, which may include use of the cryptographic key, in a protected region of memory. As a result of the tightly configured intercepts and absolute control of the protected memory regions, this activity can be guaranteed to protect both the cryptographic key and the operations results.

FIGURE 4 Thin hypervisor. The hypervisor runs in a higher privilege level than the operating system. System calls, traps, exceptions, and other interrupts, transfer control from user mode applications to the operating system. The operating system handles these conditions by requesting some service from the underlying hardware. A thin hypervisor can intercept some of those requests and handle them according to some policy.

#### 2.3 Remote Attestation and Initialization

A thin hypervisor can effectively protect the cryptographic key, after it is safely stored in privileged registers and the thin hypervisor is correctly configured. However, the target machine cannot store the cryptographic key prior to hypervisor initialization, and, thus, must obtain it from an external server at some stage.

Obviously, the external server, which we later call the *authentication authority*, has to verify that the remote machine, which is requesting the cryptographic key, is authentic and can protect this key in a potentially hostile environment. This verification process, which we call *remote attestation*, is discussed in chapter 3. Here we will outline the goals of this process.

The cryptographic keys are maintained by an authentication authority, which is equipped with facilities to verify that a thin hypervisor on a remote machine has been properly configured, such that a trusted environment is primed and can accept the cryptographic key. The vehicle to perform this remote verification is a piece of code, called a *challenge* [KJ03, SLS<sup>+</sup>05, SPvDK04]. The challenge is delivered to the remote machine during the last steps of hypervisor configuration. The remote machine is required to load and execute the challenge code, returning an attestation result to the authentication authority within a limited time-frame. The challenge calculates the checksum of the hypervisor code, but, in addition, mangles the checksum calculation with hardware-driven side effects, sampled by the challenge as it is executing. The authentication authority considers a correct response received within the allotted time-frame proof that the correct hypervisor code is executing and has true control of the remote system's hardware.

The hypervisor's code, being the only verified component, cannot call other functions. In particular, the hypervisor cannot use any of the services provided by the OS. Therefore, the part of the driver which is not included in the hypervisor is responsible for interactions with the OS. Algorithm 2.1 depicts the initialization process of the hypervisor. The process starts by obtaining the challenge code from the authentication authority. This step requires cooperation with the OS. The initialization proceeds by disabling interrupts on all execution units, thus beginning an exclusive execution of the initialization code. At this point we can safely generate sensitive information, which we do by generating random values (used later in the authentication protocol), and storing them in the debug registers. As explained in chapter 3, while one execution unit executes the challenge, other execution units must be suspended. When the challenge execution completes, its result is concatenated with the random value and encrypted using the public key of the authentication authority. Finally, the hypervisor is activated on all execution units and the control is immediately transferred to the guest. Since now the hypervisor can protect the sensitive information stored in the debug registers, we can re-enable interrupts and complete the authentication protocol. The authentication authority encrypts the cryptographic key by the random value, which is stored in the debug registers and protected by the hypervisor. The key is transferred to the driver and then to the hypervisor. The hypervisor decrypts the cryptographic key and stores it in the debug registers (the random value is erased).

#### 2.4 Thin Hypervisor Protection

The two main features of hypervisors that we actively use for protection are interrupt interception and memory virtualization. An interrupt is an event generated by the processor (or received from another processor) that requires immediate attention. The OS can specify a different handler for each such interrupt, by storing the addresses of these handlers in the interrupt descriptor table (IDT). Interrupt interception refers to hypervisor's ability to specify for each interrupt whether the hypervisor should be notified about it before the control is transferred to the interrupt handler. The hypervisor can then decide whether to ignore the interrupt or inject it back to the guest.

There are two approaches to memory virtualization: software and hardware. In software memory virtualization the hypervisor maintains a second hierarchy of virtual page tables, called *shadow page tables*, in addition to the hierarchy constructed by the OS. These shadow page tables are the ones used by the processor, while the OS believes that its hierarchy is used. The hypervisor intercepts all page faults and updates the shadow page tables according to the hierarchy maintained by the OS. Before granting the requested access rights to a page, the hypervisor verifies that this page does not contain sensitive information, which has to be protected by the hypervisor.

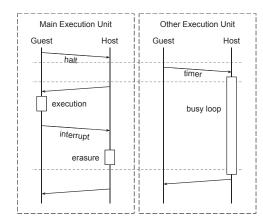

Algorithm 2.1 Initialization sequence of the hypervisor. The steps performed by the leading execution unit appear in the left column. The steps performed by all other execution units appear in the right column. The description here assumes that only two execution units are available, but it can be easily extended to any amount of execution units.

| Main Execution Unit                  | Other Execution Unit                 |  |  |

|--------------------------------------|--------------------------------------|--|--|

| 1. Send info to authority            | 1.                                   |  |  |

| 2. Receive the challenge code        | 2.                                   |  |  |

| 3. Disable interrupts                | 3. Disable interrupts                |  |  |

| 4. Generate random value R           | 4. Generate random value R           |  |  |

| 5. Store <i>R</i> in debug registers | 5. Store <i>R</i> in debug registers |  |  |

| 6. Suspend other execution units     | 6.                                   |  |  |

| 7. Execute challenge                 | 7.                                   |  |  |

| 8. Encrypt challenge result and $R$  | 8.                                   |  |  |

| 9. Resume the next execution unit    | 9.                                   |  |  |

| 10. Suspend current execution unit   | 10.                                  |  |  |

| 11.                                  | 11. Execute challenge                |  |  |

| 12.                                  | 12. Encrypt challenge result and $R$ |  |  |

| 13.                                  | 13. Resume all execution units       |  |  |

| 14. Virtualize                       | 14. Virtualize                       |  |  |

| 15. Return to guest                  | 15. Return to guest                  |  |  |

| 16. Enable interrupts                | 16. Enable interrupts                |  |  |

| 17. Send encrypted result and R      | 17.                                  |  |  |

| 18. Receive encrypted crypto key     | 18.                                  |  |  |

| 19. Deliver the key to hypervisor    | 19. Deliver the key to hypervisor    |  |  |

| 20. Decrypt the key using <i>R</i>   | 20. Decrypt the key using <i>R</i>   |  |  |

| 21. Store the key in debug registers | 21. Store the key in debug registers |  |  |

Hardware memory virtualization allows a hypervisor to define an additional translation hierarchy which maps *guest physical addresses*, i.e. physical addresses as they are perceived by the guest, to actual physical addresses. This additional hierarchy, the extended page table (EPT), allows the hypervisor to specify the access rights of each physical page. When the guest requests rights which are higher than those specified in the EPT, a vm-exit occurs, allowing the hypervisor to decide whether to grant the guest the requested privileges.

#### 2.5 Synchronization

Modern processors consist of multiple execution units. Each unit is almost completely autonomous, which means that each unit executes a separate instance of a hypervisor that share (but do not have to, in general) the code and some data structures. As we will see in chapter 4, sometimes one instance of the hypervisor has to communicate with another instance of the hypervisor. Sometimes one instance even wants to request that another instance perform some operation. This is a classic problem, which has two general solutions: a synchronous and an asynchronous one.

The asynchronous solution suggests maintaining a data structure for each instance. Each instance periodically inspects this data structure and services all requests recorded by this data structure. Other instances can submit their requests by writing them to this data structure. Hypervisor's configuration allows the specification of a maximal amount of cycles after which a vm-exit is guaranteed to happen. This mechanism can be used to perform some periodic operation in the hypervisor.

In the synchronous solution, one execution unit notifies another execution unit by sending an inter-processor interrupt (IPI). When sent, an IPI causes the destination execution unit to preempt its current execution and jump to an interrupt handler. This solution is usually much more efficient, since it shortens the request's response time. Unfortunately, it is also much more complex, since it involves modification of OS internal data structures. On 64-bit Windows, such modifications are usually detected by the PatchGuard and cause the computer to restart.

#### 3 REMOTE ATTESTATION

The problem of remote software authentication, determining whether a remote computer system is running the correct version of a software, is well known [KJ03, SLS+05, YHL+11, SPvDK04, CFPS09, SWP08, SLP+06, YWZC07]. Equipped with a remote authentication method, a service provider can prevent an unauthenticated remote software from obtaining some secret information or some privileged service. For example, only authenticated gaming consoles can be allowed to connect to the gaming networks [Ion09, Son15, Bri15], and only authenticated bank terminals can be allowed to fetch records from the bank database [Wik15].

#### 3.1 Previous Work

The research in this area can be divided into two major branches: hardware-assisted authentication and software-only authentication. Whilst, in theory, hardware-assisted authentication may provide more conclusive results regarding the authenticity of a remote machine, in practice the hardware fails to provide additional security due to the inappropriate designs of currently available operating systems [SWP08].

Hardware assisted authentication uses an external hardware component, such as Trusted Platform Module (TPM) to compute a cryptographic hash of the computer's hardware and software configuration and attest it.

Usually [Pea02, ELM<sup>+</sup>03, SZJvD04] the TPM is used as the root of the chain of trust. The TPM measures the authenticity of the BIOS. The BIOS then measures the authenticity of the boot loader and so on. Unfortunately, all common modern operating systems (e.g. Linux, Windows, OS X) allow the user to load drivers for execution with the same privileges as the operating system itself, i.e. ring 0 on x86 and x64 hardware. Malicious or buggy drivers, which are executed with high privileges, allow random code execution that makes it possible to circumvent the authenticity measurements of the TPM.

Software-only authentication usually targets a specific instruction set architecture that varies from ATMega [SPvDK04], through Pentium [KJ03] to Intel Core [YHL+11]. The authentication entails simultaneously authenticating some software component(s) or memory region, as well as verifying that the remote machine is not running in virtual or emulation mode. Software-only authentication methods may also involve a challenge code, that is sent by the authentication authority and executed on the remote system. The challenge code computes a result that is then transmitted back to the authority. The authority deems the entity to be authenticated if the result is correct and was received within a predefined time-frame. The underlying assumption, which is shared by all such authentication methods, is that only an authentic system can compute the correct result within the predefined time-frame. The methods differ in the means by which (and if) they satisfy this underlying assumption.

#### 3.2 Our Method

Kennell and Jamieson proposed [KJ03] a method that produces the result by computing a cryptographic hash of a specified memory region. Any computation on a complex instruction set architecture (Pentium in this case) produces side effects. These side effects are incorporated into the result after each iteration of the hashing function. Therefore, an adversary, trying to compute the correct result on a non-authentic system, would be forced to build a complete emulator for the instruction set architecture to compute the correct side effects of every instruction. Since such an emulator performs tens and hundreds of native instructions for every simulated instruction, Kennell and Jamieson conclude that it will not be able to compute the correct result within the predefined time-frame.

This work extends the method of Kennel and Jamieson, and adapts it to modern processors. A detailed discussion of all the extensions can be found in [PI, PIII]. Figure 5 depicts the interaction between the authentication authority and the target computer. The initial messages of the protocol carry information about the current configuration of the target machine. Following this exchange, the authentication authority transmits a message containing the challenge code to be executed on the target machine. The target machine executes the challenge, which computes a result that is a cryptographic hash of some memory region, possibly with some additional information. The target machine concatenates a randomly generated number to the result, encrypts both values with the public key of the authentication authority, and transmits the encrypted message. The authentication authority verifies that the result is correct and was received within a predefined time-frame. If both are true the target machine is considered authentic. The authentication authority then shares some secret information with the target machine. This secret information constitutes a proof of target's authenticity. The authentication authority encrypts the secret information with the random value from message (3) acting as an encryption key, and transmits the encrypted

FIGURE 5 The attestation protocol between the authentication authority and the target machine. The protocol consists of four messages. The first two messages are sent unencrypted, while the two last messages are encrypted. The third message is encrypted by the public key of the authentication authority and the fourth message is encrypted by the random value transmitted in the third message.

message to the target machine.

During every communication session, the authentication authority selects a random challenge from the set of challenges that suit the target's configuration. During the construction of the challenge repository, the authentication authority attaches additional information to each challenge — for example, the expected result of the challenge and the maximal amount of time needed for its execution. The authentication authority denies target machines whose results differ from the expected, or were reported outside the predefined time-frame.

The population of the challenge repository is a randomized iterative process, which generates a challenge (the randomized part), computes its result, and stores the information in the repository.

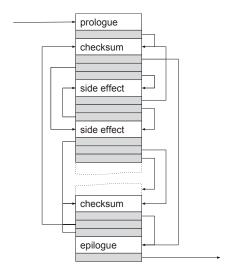

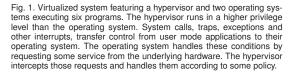

Figure 6 presents the general structure of a challenge, which mostly consists of checksumming and side effect accumulating blocks. Two special blocks that appear in all challenges are the prologue and the epilogue. The prologue block is the entry point of the challenge. This block is responsible for setting up an appropriate execution environment for the challenge (explained below). The prologue then proceeds by initializing the result variable (actually, register) to zero and transferring control to another block: a side effect accumulating block or a checksumming block. A side effect accumulating block retrieves information about the current internal state of the processors and incorporates it into the result variable. Then, depending on the value of the result, it jumps to one of the three predefined blocks. A checksumming block advances (in a pseudo-random fashion) a memory pointer to a new location, reads the content at this location and incorporates it into the result. If the final location was reached, the checksumming block jumps to the epilogue block, otherwise it jumps to one of the three predefined blocks

FIGURE 6 The structure of the attestation challenge. The white rectangles, together with the gray rectangles beneath them, represent the challenge blocks. Each gray rectangle is a conditional control transfer, which is represented by an arrow to another block. The white rectangles are the blocks themselves, which compute checksum or incorporate side effects.

based on the result. The epilogue block restores the execution environment and returns the computed result to the caller.

#### 3.3 Side Effects

Every instruction that is executed by a processor modifies its internal state. Some modifications result from the definition of the instruction operations; others are performed by the processor to improve performance, e.g., cache population; or for debugging and profiling purposes, e.g., L3 cache miss count. Previously, processors were allowed to observe the state of side effects directly. Current versions of processors provide a different mechanism — performance counters. The processor defines pairs of registers: an event selection register, which allows the software to specify the execution event to be counted, and a monitoring counter register, which is increased on each occurrence of the event specified by the first register. The values of the counter registers can be considered the state of the side effect and as such can be incorporated into the result by the side effect accumulating blocks.

It is desirable to construct the challenge in a way that maximizes the side effects produced by its execution. One of the side effects that were considered in [KJ03] is the TLB management system. TLBs store translations of virtual addresses to physical addresses of pages that were recently accessed. Modern pro-

cessors contain separate TLBs for instructions and data as well as a shared TLB of a higher level, which is larger but slower. When a new translation needs to be stored in a TLB with no free slots, one of the slots is evicted according to some policy, which varies between processors. In order to achieve high utilization of the TLBs the authors of [KJ03] propose to map a large virtual memory region that maps a smaller physical memory region that is to be authenticated. The challenge then can compute the hash by reading the contents of the physical memory region through different pages of the virtual memory region, thus fully utilizing the DTLB and inducing more side effects. In order to fully utilize the ITLB, we map the challenge blocks to different virtual pages and use their addresses in those pages as the control transfer destinations.

As we have seen in chapter 2, a hypervisor can prevent the virtual environment from accessing some physical pages. Moreover, the virtual environment will be unaware of this situation. In other words, a hypervisor can deceive the virtual environment into thinking that it has full control of the underlying hardware and no other software is currently being executed. Obviously a challenge, being part of the virtual environment, can be deceived as well.

Fortunately, some events are intercepted by hypervisors unconditionally. In particular, on processors manufactured by Intel, execution of the CPUID instruction always causes a vm-exit. On vm-exit, the processor loads the first instruction of the function whose address is specified in VMCS. This behavior alone will affect some of the caches, regardless of the actual implementation of the function. The lookup of the address modifies at least one entry of the ITLB and the higher level TLB (STLB). Fetching the first instruction modifies at least one entry in the instruction cache, L2 cache and L3 cache. In addition, execution of such an instruction takes much more time when a VMM is active. Therefore, in challenges, which are targeted at modern processors, we widen the variety of blocks by adding blocks that produce events whose interception cannot be disabled. An example of such a block is a block that contains a CPUID instruction.

In modern processors, the number of possible performance events greatly outnumber the available hardware counter circuits. Most processor models are restricted to 2-4 individual performance counters. Therefore, it is possible to dynamically link an available performance counter to a specific performance event. Once linked, the performance counter counts the number of events that occurred.

One of the challenge's goals is to determine if the remote machine is executing under emulation or not. Two factors are measured to determine this: the challenge result and the challenge's elapsed execution time. Since the result of a challenge is affected by the values of performance counters at different execution points, an emulator is forced to keep track of their values. Even assuming that such a feat is possible with regard to one of the side effect modules, referencing several modules in a single challenge would necessarily amplify the elapsed execution time differences, since these emulations are mostly orthogonal.

It is, therefore, desirable to utilize a large variety of performance measurements. Each such performance measurement increases the execution time of an emulator, but has no effect on a non-emulated system. A clear deficiency with

respect to this is the low ratio of available performance counters to possible performance events that can be measured. We suggest to overcome this deficiency by using *chained performance-counters*.

The idea is to monitor many side effect inducing modules with a much smaller number of available performance counters, by shifting the counters from one module to the next according to a set of deterministic rules. All processor components that generate side effects are initialized to a known state before the challenge execution begins. When challenge execution flow reaches a determinable point, the contents of each side effect inducing module is deterministic and repeatable regardless of our measurement, i.e whether a performance counter was used to monitor its side effects or not. It follows that a performance counter can be connected to the module to count new events. The new events will occur deterministically for the active challenge given the new determinable state.

As a result, monitoring performance events on multiple modules, using a single performance counter to measure the performance events of these modules, during several separate time intervals, will require a masquerading emulator to emulate all side effect inducing modules to achieve the correct result.

#### 4 NATIVE CODE EXECUTION

Despite the rising popularity of managed execution environments, such as Java and .NET, native programming languages, such as C and C++, are still widely used, especially in areas that require high performance, e.g. Web browsing, image and video editing, gaming, etc. Many of these programs contain proprietary algorithms and licensing schemes, which might be subject to reverse engineering and modification. The main countermeasure which is currently available is obfuscation. As discussed in chapter 1 this measure can be easily circumvented by a skilled professional and is, therefore, unreliable.

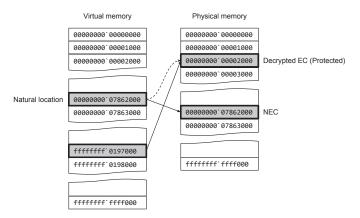

We propose to protect the sensitive parts of a native program by encrypting them. Encryption and execution of encrypted code require special software components. This chapter summarizes the detailed description of these components provided by [PVII]. The relationship between the components is depicted in Figure 7. The general purpose and the abilities of a hypervisor, as well as the necessity for a driver wrapper, were discussed in chapter 2. The attestation software was discussed in chapter 3.

#### 4.1 Encryption Tool

The encryption tool is responsible for encryption of selected functions in a program. The user selects the functions to be encrypted by specifying their names in a configuration file. A *map file* or a *debug symbols file*, which are produced by a compiler, can then be used to translate the names of the functions to their locations in the program file.

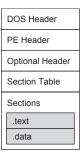

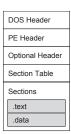

On Windows, program files (executables and dynamic libraries) are stored in Portable Executable (PE) format. Figure 8 depicts the structure of a PE file. The different headers define the expected location of the PE file when loaded to memory, sizes and positions of various data structures inside the PE file, the number of sections contained in this PE file, etc. The section table contains a description of each of the sections contained in the PE file. Following the section

FIGURE 7 Native code protection system. The original program is encrypted before its distribution. The encryption key is stored in the attestation server, which delivers it to the hypervisor in the target machine upon successful attestation. The hypervisor is initialized by a driver, which also hosts the code of the hypervisor.

table are the sections themselves. Sections vary in their structure and purpose: the .text section contains the code of the program, the .data section contains its constants. Other sections may contain information about resources (images and sounds) embedded in the PE file or information used during exception delivery.

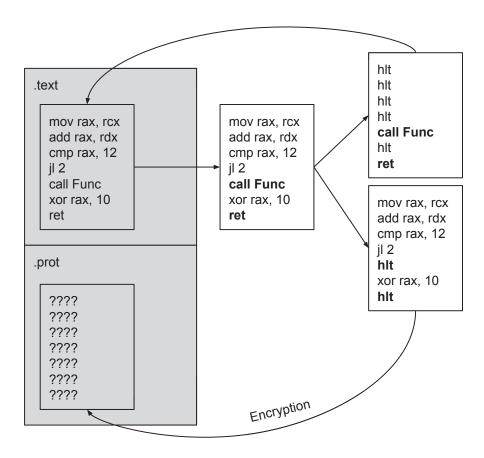

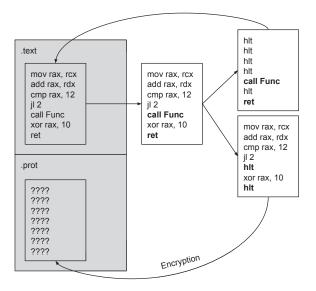

The encryption tool modifies the given PE file by introducing a new section, which stores the selected functions in encrypted form. The instructions of the original functions are partially replaced by an exception-inducing instruction. We propose to use either the *halt* instruction or the *software breakpoint* instruction. The halt instruction is a privileged instruction, which deactivates the current processor when executed in kernel mode, but generates a general protection fault when executed in user mode. The software breakpoint instruction generates a

FIGURE 8 Structure of a Windows PE file. The structure contains a variable number of sections. Two of the most common sections are presented.

breakpoint trap when executed in either kernel or user modes. Faults and traps, being types of interrupts, can be intercepted by a hypervisor, which can then decrypt and execute the original encrypted function. Another benefit of the halt and the software breakpoint instructions is that they can be represented by a single byte (0xF4 for halt and 0xCC for software breakpoint), thus allowing them to fully cover any number of bytes. The software breakpoint instruction is superior to the halt instruction in that it generates an interrupt not only in user mode but also in kernel mode.

As will be explained in section 4.2.1, it is highly important to intercept control transfers that leave the encrypted function. The encryption tool disassembles the function to be encrypted and inspects its instructions. The instructions then are classified as *encryptable* and *non-encryptable*. The encryption tool classifies an instruction as non-encryptable if it might transfer control out of the encrypted function. For example, the *ret* and the *call* instructions are always classified as non-encryptable, but the *jmp* instruction is classified as non-encryptable only if its destination lies outside the function's bounds, or if the destination cannot be determined statically (if it is a register, for instance).

The encryption tool produces two copies of the original function, the encryptable copy (EC) and the non-encryptable copy (NEC). In the EC all the non-encryptable instructions are replaced by the halt or the software breakpoint instructions. Then the encryption tool encrypts the EC and stores it in the new section. In the NEC all the encryptable instructions are replaced by the halt or the software breakpoint instructions. Then the encryption tool replaces the original function by the NEC. Figure 9 presents an example of such transformation.

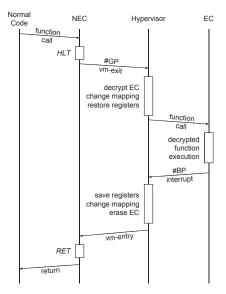

#### 4.2 Encrypted Program Execution

In order to execute an encrypted program, the user must first install the driver, which wraps the hypervisor. The driver monitors the PE files loaded by the OS, and keeps track of PE files that contain the special section. When the first such PE file is loaded, the driver initializes the hypervisor. During the initialization, the driver communicates with the authentication authority, passes verification, obtains the cryptographic key, and enters a virtualized state. Chapter 2 provides a detailed description of this process.

The hypervisor is configured to intercept the general protection fault. When a protected program transfers control to an encrypted function, the processor attempts to execute the halt instruction, which induces a general protection fault, transferring control to the hypervisor. General protection faults rarely occur during the normal course of program execution, since they usually cause the program to terminate abruptly. Nevertheless, the hypervisor uses the data structures prepared by the driver to test whether the general protection fault occurred during execution of an encrypted function.

The hypervisor injects the interrupt back to the guest if it was not caused by

FIGURE 9 Example of an encryption process of a single function. The encryption begins by classifying instruction is encryptable (normal face) and non-encryptable (bold face), and creating to copies. The complementary instructions in each copy are replaced by halts. Finally, one copy is written over the original functions, and the other is encrypted and added to the special section.

an encrypted function execution. Otherwise, the hypervisor decrypts the function and starts its execution. Since during its execution, the function is stored in memory in unencrypted form, it is highly important to ensure that no other code has access to the unencrypted instructions of the function. We note that in modern processors, several execution units (logical processors) can execute programs concurrently. Therefore, we must ensure that programs executed by all execution units have no access to the unencrypted instructions.

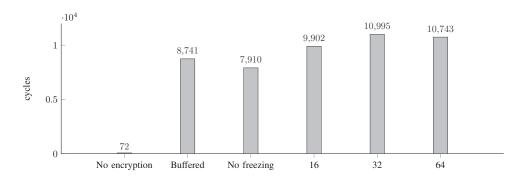

We present two approaches to sensitive functions execution: in-place execution and buffered execution.

#### 4.2.1 In-place Execution

According to this approach the hypervisor can be in one of two states: cold or hot. In the cold state the memory does not contain any sensitive information and only the cryptographic key and the hypervisor's state must be protected. This is the regular mode of operation described in chapter 2. The hypervisor switches to the hot state when the memory contains sensitive information, which cannot be protected by a regular memory protection technique (using EPT), since its physical location is not known (or not constant). This switch occurs when the hypervisor starts execution of an encrypted function.

In the following description, we assume that the encryption tool uses halt as a replacement instruction, but the same is true for the software breakpoint instruction.

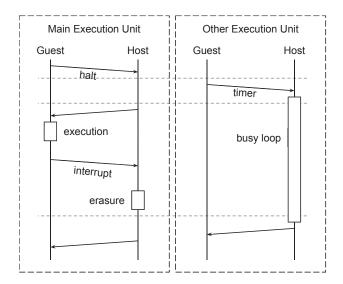

At the initialization the hypervisor's state is set to cold. In this state, in addition to the regular protection means described in chapter 2, the hypervisor intercepts general protection faults. An encrypted function which was overwritten by the NEC consists mainly of halt instructions. Execution of these instructions induces a general protection fault, which causes a vm-exit and transfers control to the hypervisor. The hypervisor inspects the source of the general protection fault, and fetches the EC that corresponds to the NEC. Then the hypervisor switches to hot mode and decrypts the EC to its natural location, currently occupied by the NEC (the NEC is copied to a different location for future use).

During the switch to hot mode, the hypervisor freezes all other execution units, and configures itself to intercept all interrupts. This behaviour guarantees that the function in its decrypted form cannot be read by any other, potentially malicious, code, simply because no other code can run in hot mode. We note that all the control transfer instructions in the EC are replaced by the halt instruction, which induces a vm-exit.

When a vm-exit occurs in hot mode, the hypervisor switches to cold mode. First, the decryption function is replaced by the corresponding NEC. Then the hypervisor unfreezes all the execution units, configures itself to intercept only general protection faults, and returns to the guest. Figure 10 depicts the control flow during encrypted function execution.

We suggest freezing other execution units by inducing a vm-exit on each execution unit, and running a busy loop until the hypervisor switches back to

FIGURE 10 Example of encrypted function execution. The figure depicts two execution units, each with two alternating states: guest and host. The dashed horizontal lines are synchronization barriers, i.e. everything above the line is guaranteed to complete before anything below the line starts.

cold mode. A vm-exit can be induced either implicitly on a timer, or explicitly by sending an inter-processor interrupt (IPI). The former solution is much easier to implement but the latter solution is much more efficient.

The hypervisor intercepts interrupts in hot mode by replacing the original interrupt descriptor table (IDT) of the OS with a specially crafted IDT. In this special IDT each handler induces a vm-exit — for example, by executing the CPUID instruction. The hypervisor intercepts this instruction, realizes that an interrupt at vector N occurred and switches to cold mode. The hypervisor proceeds by installing the original IDT and moving the instruction pointer of the guest to point to the Nth interrupt handler of the original IDT.

#### 4.2.2 Buffered Execution

This approach is more efficient but potentially less secure than the in-place execution. According to this approach, the decrypted functions are executed inside the hypervisor. As a consequence these functions have the same privileges as the hypervisor itself. In particular, they can read and write memory, which is otherwise inaccessible to any code external to the hypervisor. One can argue that it is impossible for an adversary to replace the EC with a random code, without knowing the cryptographic key. Unfortunately, it is possible that some memory manipulation can be performed indirectly by modifying the data on which the encrypted function works. Although possible, it seems to be extremely difficult to manipulate the behaviour of an unknown code through its data.

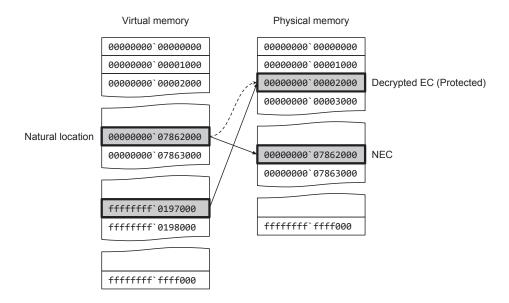

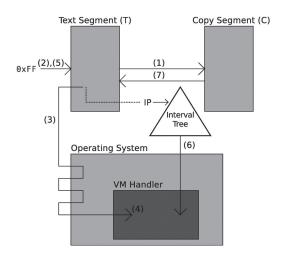

FIGURE 11 Memory layout during buffered execution. The functions resided at virtual address 7862000, which is mapped to the physical address 7862000 (a coincidence). The encrypted code is decrypted to virtual address ffffffff0197000 which is mapped to the physical address 2000. The hypervisor changes the mapping of the virtual address 7862000 to map the physical address 2000.

In the following description, we assume that the encryption tool uses halt as a replacement instruction for NECs and software breakpoint as a replacement instruction for ECs.

In this approach, the hypervisor has only one state, in which it protects itself as described in chapter 2. In addition, the hypervisor configures itself to intercept general protection faults. Execution of halt instructions induces a general protection fault, which causes a vm-exit and transfers control to the hypervisor. The hypervisor inspects the source of the general protection fault, and fetches the EC that corresponds to this NEC.

When the EC is resolved, the hypervisor decrypts it to a pre-allocated memory buffer, which is protected by the hypervisor. Since the decrypted instructions are inaccessible by any other execution unit (in guest mode), there is no need to suspend them. Likewise, since the encrypted instructions are executed inside the hypervisor, there is no need to modify the IDT of the guest. Finally, there is no need to perform the costly transitions to and from the guest after every decryption. All these improve the overall performance of the system by a large factor.

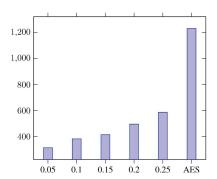

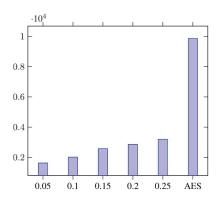

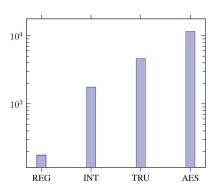

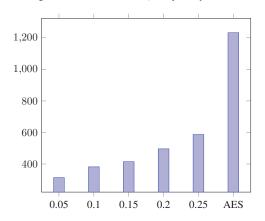

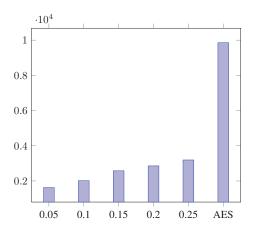

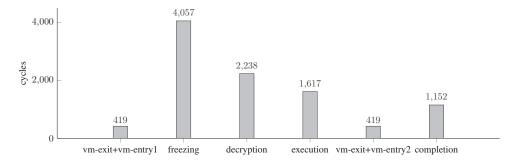

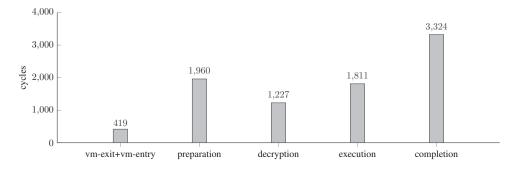

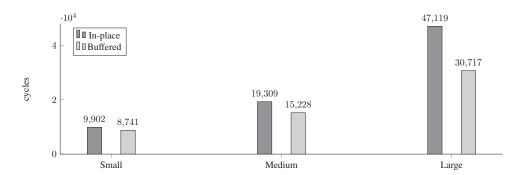

The x86 instruction set architecture defines many memory access instructions as *relative*, meaning that their arguments should not be interpreted as actual memory locations but rather that they should be interpreted as offsets from the current value of the instruction pointer. As a consequence, the same instruction may have different interpretations when executed from different locations.